The ADC produces a signal on the output pins on both high and low clock pulses as well as passes on the CLK IN for use by the FPGA. Texas instuments provides a document describing the method they use to disentagle the bits and reassemble them properly on the FPGA side and code which can generate block function for use in a Quartus II project, these can be found here. This leaves the problem of discovering which pins put out data on the ADC and which pins take in data on the FPGA Dev Board to the user.

In the ADC schemaitc pdf located in this archive, a user can find that pins in the range 32-84 are used for transmitting bits of data (P) and their compliment (M) and that pin 56 provides the clock output from the ADC. Following the traces over the bridge in the schematic located in this archive the FPGA recives the data on pins in the range from 78-122 and the clock on pin 156. The names of these pins can be looked up on page 37 and 39 of the Cyclone V Dev Board Guide and properly assigned in the quartus project.

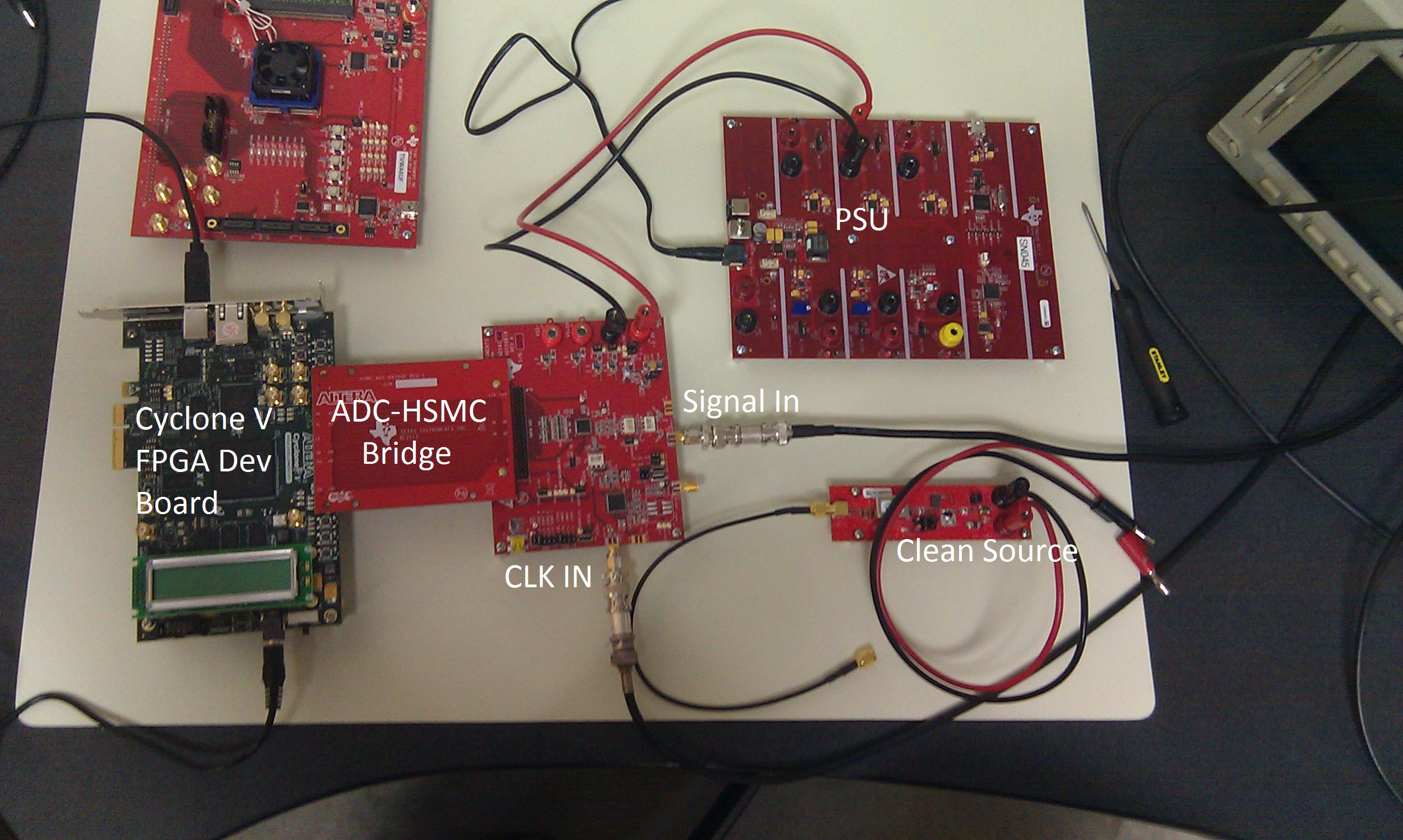

With this information I produced a simple block schematic that includes the proper pin inputs and 5 LEDs to verify working conditions in the future. The MY_FPGA_TOP_LEVEL block is an altered version of the original from Texas Instruments that took in data from an ADC and output it on a DAC. All output fuctionality was removed and now the data comes in and the bits are properly interleaved from the high and low samplings to create a 12 bit reading.

The next challenge is to verify that information is being stored off the ADC and then to determine if that information is useful. To accomplish the first part of this task, a memory block will be set up to take the data as it gets output from MY_FPGA_TOP_LEVEL and store it. With an idicator light to verify when the memory is full this will provide an indicator that data is at least being clocked though. To get the data off the FPGA a JTAG chain must be used. Luckily Ian does the same thing with his system and I can ask him for some guidance since this part is supposed to be difficult.